## 2N5441-2N5446 T6420 SERIES

## **40A SILICON TRIACS**

#### **FEATURES**

- Available as "HR" (high reliability) screened per MIL-PRF-19500, JANTX level. Add "HR" suffix to base part number.

- Available as non-RoHS (Sn/Pb plating), standard, and as RoHS by adding "-PBF" suffix.

#### **MAXIMUM RATINGS**

| Rating                                                                                                                                                                                  | Symbol                                     | 2N5441<br>2N5444<br>T6420B | 2N5442<br>2N5445<br>T6420D | 2N5443<br>2N5446<br>T6420M | Unit    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|----------------------------|----------------------------|----------------------------|---------|

| Repetitive peak off-state voltage <sup>(1)</sup> Gate open, T <sub>J</sub> = -65 to 100°C                                                                                               | V <sub>DROM</sub>                          | 200                        | 400                        | 600                        | V       |

| RMS on-state current (Conduction angle = 360°) $T_{C} = 70^{\circ}\text{C (press-fit type)}$ $T_{C} = 65^{\circ}\text{C (stud type)}$ $T_{C} = 60^{\circ}\text{C (isolated stud type)}$ | I <sub>T(RMS)</sub>                        |                            | 40<br>40<br>40             |                            | А       |

| Peak surge (non-repetitive) on state current For one cycle of applied principal voltage 60Hz (sinusoidal) 50Hz (sinusoidal)                                                             | I <sub>TSM</sub>                           |                            | 300<br>265                 |                            | А       |

| Rate of change of on-state current $V_{DM} = V_{DROM}, I_{GT} = 200 mA, t_r = 0.1 \mu s$                                                                                                | di/dt                                      |                            | 100                        |                            | A/μs    |

| Fusing current T <sub>J</sub> = -65° to 110°C, t = 1.25 to 10ms                                                                                                                         | l <sup>2</sup> t                           | 450                        |                            | A <sup>2</sup> s           |         |

| Peak gate trigger current <sup>(2)</sup> For 1μs maximum                                                                                                                                | rurrent <sup>(2)</sup> I <sub>GTM</sub> 12 |                            | А                          |                            |         |

| Gate power dissipation Peak (for 10μs maximum, I <sub>GTM</sub> ≤ 4A Average                                                                                                            | P <sub>GM</sub>                            |                            | 40<br>0.75                 |                            | W       |

| Storage temperature range                                                                                                                                                               | T <sub>stg</sub>                           |                            | -65 to 150                 |                            | °C      |

| Operating temperature range                                                                                                                                                             | T <sub>c</sub>                             |                            | -65 to 110                 |                            | °C      |

| Terminal temperature (during soldering) For 10 s maximum (terminals and case)                                                                                                           | T <sub>T</sub>                             |                            | 225                        |                            | °C      |

| Maximum stud torque                                                                                                                                                                     | r <sub>s</sub>                             |                            | 50                         |                            | In. lb. |

Note 1: For either polarity of main terminal 2 voltage  $(V_{MT2})$  with reference to main terminal 1. Note 2: For either polarity of gate voltage  $(V_G)$  with reference to main terminal 1.

# 2N5441-2N5446 T6420 SERIES

## **40A SILICON TRIACS**

#### ELECTRICAL CHARACTERISTICS @ 25°C unless otherwise noted

| ELECTRICAL CHARACTERISTICS & 25 CUITICS STREET                                          |                   | Limits                                   |      |      |       |

|-----------------------------------------------------------------------------------------|-------------------|------------------------------------------|------|------|-------|

| Characteristic                                                                          | Symbol            | For all types unless otherwise specified |      |      | Units |

|                                                                                         |                   | Min                                      | Тур  | Max  |       |

| Peak off-state current <sup>(1)</sup>                                                   |                   |                                          | 0.3  | 4    | m A   |

| Gate open, T <sub>J</sub> = 110°C, V <sub>DROM</sub> = maximum rated value              | I <sub>DROM</sub> | -                                        | 0.2  | 4    | mA    |

| Maximum on-state voltage <sup>(1)</sup>                                                 |                   |                                          |      |      |       |

| $I_T = 100A(peak), T_C = 25^{\circ}C$                                                   | $V_{TM}$          | -                                        | 1.7  | 2    | V     |

| $I_T = 56A(peak), T_C = 25^{\circ}C$                                                    |                   | -                                        | 1.5  | 1.85 |       |

| DC holding current <sup>(1)</sup>                                                       |                   |                                          |      |      |       |

| Gate open, initial principal current = $500mA(dc)$ , $V_D = 12V$                        |                   |                                          |      |      | mA    |

| T <sub>C</sub> = 25°C                                                                   | I <sub>HO</sub>   | -                                        | 25   | 60   | IIIA  |

| T <sub>C</sub> = -65°C                                                                  |                   | -                                        | -    | 100  |       |

| Critical rate of rise of commutation voltage <sup>(1)</sup>                             |                   |                                          |      |      |       |

| For $V_D = V_{DROM}$ , $I_{T(RMS)} = 40A$ , commutating                                 |                   |                                          |      |      |       |

| di/dt = 22A/ms, gate unenergized                                                        | dv/dt             |                                          |      |      | V/µs  |

| $T_C = 70^{\circ}C$ (press fit type)                                                    | uv/ut             | 5                                        | 30   | -    | ν/μς  |

| $T_c = 65^{\circ}C$ (stud type)                                                         |                   | 5                                        | 30   | -    |       |

| $T_C = 60$ °C (isolated-stud types)                                                     |                   | 5                                        | 30   | -    |       |

| Critical rate of rise of off-state voltage <sup>(1)</sup>                               |                   |                                          |      |      |       |

| For V <sub>D</sub> = V <sub>DROM</sub> , exponential voltage rise, gate open            |                   |                                          |      |      |       |

| T <sub>C</sub> = 110°C:                                                                 | dv/dt             |                                          |      |      | V/µs  |

| 2N5441, 2N5444, T6420B                                                                  | uv/ut             | 50                                       | 200  | -    | ν/μς  |

| 2N5442, 2N5445, T6420D                                                                  |                   | 30                                       | 150  | -    |       |

| 2N5443, 2N5446, T6420M                                                                  |                   | 20                                       | 100  | -    |       |

| DC trigger current                                                                      |                   |                                          |      |      |       |

| $(V_D = 12V, R_L = 30\Omega, T_C = 25^{\circ}C)$                                        |                   |                                          |      |      |       |

| MT2(+),G(+)                                                                             |                   | -                                        | 15   | 50   |       |

| MT2(-), G(-)                                                                            |                   | -                                        | 20   | 50   |       |

| MT2(+), G(-)                                                                            |                   | -                                        | 30   | 80   |       |

| MT2(-), G(+)                                                                            | I <sub>GT</sub>   | -                                        | 40   | 80   | mA    |

| $(V_D = 12V, R_L = 30\Omega, T_C = -65^{\circ}C)$                                       |                   |                                          |      |      |       |

| MT2(+),G(+)                                                                             |                   | -                                        | -    | 125  |       |

| MT2(-), G(-)                                                                            |                   | -                                        | -    | 125  |       |

| MT2(+), G(-)                                                                            |                   | -                                        | -    | 240  |       |

| MT2(-), G(+)                                                                            |                   | -                                        | -    | 240  |       |

| DC gate trigger voltage <sup>(1)(2)</sup>                                               |                   |                                          |      |      |       |

| $V_D = 12V(dc), R_L = 30\Omega$                                                         |                   |                                          |      |      |       |

| T <sub>c</sub> = 25°C                                                                   | $V_{GT}$          | -                                        | 1.35 | 2.5  | V     |

| T <sub>c</sub> = -65°C                                                                  |                   | -                                        | 1.80 | 3.4  |       |

| $V_D = V_{DROM}, R_L = 125\Omega, T_C = 110^{\circ}C$                                   |                   | 0.2                                      | -    | -    |       |

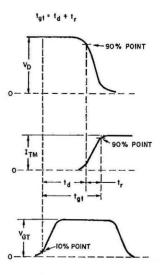

| Gate controlled turn on time                                                            |                   |                                          |      |      |       |

| (Delay time + rise time)                                                                | t <sub>gt</sub>   | -                                        | 1.7  | 3    | μs    |

| $V_D = V_{DROM}$ , $I_{GT} = 200$ mA, $t_r = 0.1$ µs, $I_T = 60$ A(peak), $T_C = 25$ °C |                   |                                          |      |      |       |

# 2N5441-2N5446 T6420 SERIES

## **40A SILICON TRIACS**

| Thermal resistance, junction to case, steady state |                  |   |   |     |       |

|----------------------------------------------------|------------------|---|---|-----|-------|

| Press fit types                                    | D                | - | - | 0.8 | °C/W  |

| Stud types                                         | R <sub>OJC</sub> | - | - | 0.9 | C/ VV |

| Isolated stud types                                |                  | - | - | 1   |       |

Note 1: For either polarity of main terminal 2 voltage  $\{V_{MT2}\}$  with reference to main terminal 1. Note 2: For either polarity of gate voltage  $\{V_G\}$  with reference to main terminal 1.

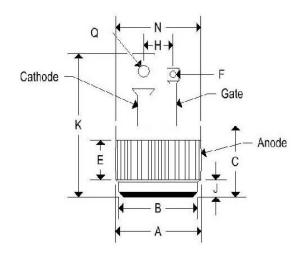

#### **MECHANICAL CHARACTERISTICS**

| Case Digi PF1 (2N5441-2N5443) |                 |

|-------------------------------|-----------------|

| Marking                       | Alpha-numeric   |

| Polarity                      | Cathode is stud |

|   | DIGI PF1 |                    |        |        |  |  |  |

|---|----------|--------------------|--------|--------|--|--|--|

|   | Inc      | Inches Millimeters |        |        |  |  |  |

|   | Min      | Max                | Min    | Max    |  |  |  |

| Α | 0.501    | 0.505              | 12.730 | 12.830 |  |  |  |

| F | 34.      | 0.160              | 14.    | 4.060  |  |  |  |

| G | 0.085    | 0.095              | 2.160  | 2.410  |  |  |  |

| Н | 0.060    | 0.070              | 1.520  | 1.780  |  |  |  |

| J | 0.300    | 0.350              | 7.620  | 8.890  |  |  |  |

| K | 12       | 1.050              | 14     | 26.670 |  |  |  |

| L | 7-       | 0.670              | -      | 17,020 |  |  |  |

| Q | 0.055    | 0.085              | 1.400  | 2.160  |  |  |  |

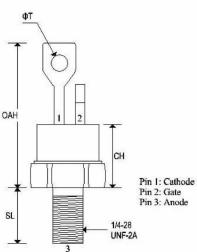

#### **MECHANICAL CHARACTERISTICS**

| Case TO-48 (2N5444-2N5446) |                 |

|----------------------------|-----------------|

| Marking                    | Alpha-numeric   |

| Polarity                   | Cathode is stud |

# CD HF

# 2N5441-2N5446 T6420 SERIES

**40A SILICON TRIACS**

|                 | TO-48              |       |        |        |

|-----------------|--------------------|-------|--------|--------|

|                 | Inches Millimeters |       |        |        |

|                 | Min                | Max   | Min    | Max    |

| CD              | ¥                  | 0.543 | ï      | 13.793 |

| CH              | ī                  | 0.550 | 1      | 13.970 |

| HF              | 0.544              | 0.563 | 13.817 | 14.301 |

| OAH             |                    | 1.193 | *      | 30.303 |

| SL              | 0.422              | 0.453 | 10.718 | 11.507 |

| ΦТ              | 0.125              | 0.165 | 3.175  | 4.191  |

| ΦT <sub>1</sub> | 0.060              | 0.075 | 1.524  | 1.905  |

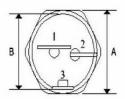

Note: Contour and angular orientation of terminals 1 and 2 with respect to hex portion and to each other are optional.

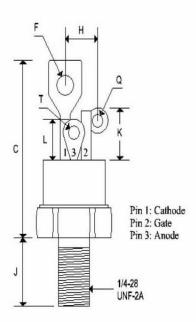

#### **MECHANICAL CHARACTERISTICS**

| Case TO-48 ISO (T6420 Series) |                 |

|-------------------------------|-----------------|

| Marking Alpha-numeric         |                 |

| Polarity                      | Cathode is stud |

# 40A SILICON TRIACS

2N5441-2N5446

T6420 SERIES

|   | TO-48 ISO |       |             |        |  |  |

|---|-----------|-------|-------------|--------|--|--|

|   | Inc       | hes   | Millimeters |        |  |  |

|   | Min       | Max   | Min         | Max    |  |  |

| Α | 0.551     | 0.559 | 14.000      | 14.200 |  |  |

| В | 0.501     | 0.505 | 12.730      | 12.830 |  |  |

| С | -         | 1.280 |             | 32.510 |  |  |

| F | -         | 0.160 | UES.        | 4.060  |  |  |

| Н | -         | 0.265 | -           | 6.730  |  |  |

| J | 0.420     | 0.455 | 10.670      | 11.560 |  |  |

| K | 0.300     | 0.350 | 7.620       | 8.890  |  |  |

| L | 0.255     | 0.275 | 6.480       | 6.990  |  |  |

| Q | 0.055     | 0.085 | 1.400       | 2.160  |  |  |

| I | 0.135     | 0.150 | 3.430       | 3.810  |  |  |

## 2N5441-2N5446 T6420 SERIES

## **40A SILICON TRIACS**

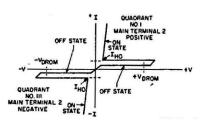

Fig. 1 - Principal voltage-current characteristic.

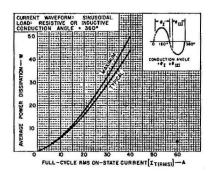

Fig. 2 - Power dissipation vs. on-state current.

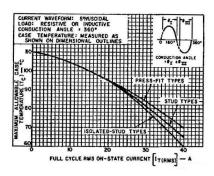

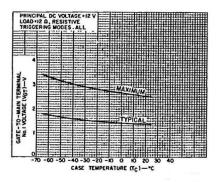

Fig. 3 - Maximum allowable case temperature vs. on-state current.

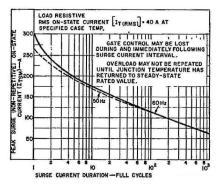

Fig. 4 - Peak surge on-state current vs. surge current duration.

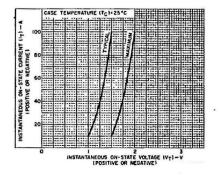

Fig. 5 - On-state current vs. on-stage voltage.

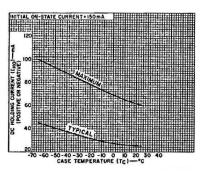

Fig. 6 - DC holding current vs. case temperature.

## 2N5441-2N5446 T6420 SERIES

## **40A SILICON TRIACS**

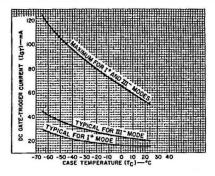

Fig. 7 - DC gate-trigger current vs. case temperature (I\* & III- modes).

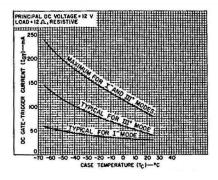

Fig. 8 - DC gate-trigger current vs. case temperature (I- & III-modes).

Fig. 9 - DC gate trigger voltage vs. case temperature.

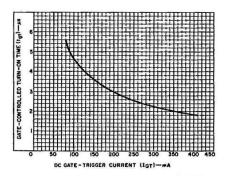

Fig. 10 - Turn-on time vs. gate-trigger current.

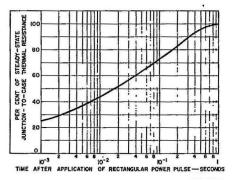

Fig. 11 - Transient junction-to-case thermal reistance vs. time for press-fit and stud types.

## 2N5441-2N5446 T6420 SERIES

## **40A SILICON TRIACS**

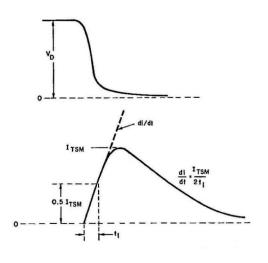

Fig. 12 - Rate of change of on-state current with time (defining di/dt).

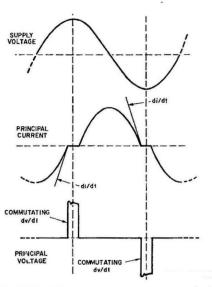

Fig. 13 - Relationship between supply voltage and principal current (inductive load) showing reference points for definition of commutating voltage (dv/dt).

Fig. 14 - Relationship between off-state voltage, on-state current, and gate-trigger voltage showing reference points for definition of turn-on time  $(t_{a1})$ .